Merge pull request #10653 from dylad/pr/saml1x_support

cpu/saml1x: add support for SAML10 and SAML11 MCUs (Cortex-M23)

This commit is contained in:

commit

7e3c382547

3

boards/common/saml1x/Makefile

Normal file

3

boards/common/saml1x/Makefile

Normal file

@ -0,0 +1,3 @@

|

|||||||

|

MODULE = boards_common_saml1x

|

||||||

|

|

||||||

|

include $(RIOTBASE)/Makefile.base

|

||||||

3

boards/common/saml1x/Makefile.dep

Normal file

3

boards/common/saml1x/Makefile.dep

Normal file

@ -0,0 +1,3 @@

|

|||||||

|

ifneq (,$(filter saul_default,$(USEMODULE)))

|

||||||

|

USEMODULE += saul_gpio

|

||||||

|

endif

|

||||||

13

boards/common/saml1x/Makefile.features

Normal file

13

boards/common/saml1x/Makefile.features

Normal file

@ -0,0 +1,13 @@

|

|||||||

|

# Put defined MCU peripherals here (in alphabetical order)

|

||||||

|

FEATURES_PROVIDED += periph_adc

|

||||||

|

FEATURES_PROVIDED += periph_i2c

|

||||||

|

FEATURES_PROVIDED += periph_rtc

|

||||||

|

FEATURES_PROVIDED += periph_rtt

|

||||||

|

FEATURES_PROVIDED += periph_spi

|

||||||

|

FEATURES_PROVIDED += periph_timer

|

||||||

|

FEATURES_PROVIDED += periph_uart

|

||||||

|

|

||||||

|

# The board MPU family (used for grouping by the CI system)

|

||||||

|

FEATURES_MCU_GROUP = cortex_m23

|

||||||

|

|

||||||

|

include $(RIOTCPU)/saml1x/Makefile.features

|

||||||

12

boards/common/saml1x/Makefile.include

Normal file

12

boards/common/saml1x/Makefile.include

Normal file

@ -0,0 +1,12 @@

|

|||||||

|

# define the cpu used by the saml11 board

|

||||||

|

export CPU = saml1x

|

||||||

|

|

||||||

|

# set edbg device type

|

||||||

|

EDBG_DEVICE_TYPE = mchp_cm23

|

||||||

|

|

||||||

|

USEMODULE += boards_common_saml1x

|

||||||

|

|

||||||

|

include $(RIOTMAKE)/boards/sam0.inc.mk

|

||||||

|

|

||||||

|

# add the common header files to the include path

|

||||||

|

INCLUDES += -I$(RIOTBOARD)/common/saml1x/include

|

||||||

44

boards/common/saml1x/board.c

Normal file

44

boards/common/saml1x/board.c

Normal file

@ -0,0 +1,44 @@

|

|||||||

|

/*

|

||||||

|

* Copyright (C) 2019 Mesotic SAS

|

||||||

|

*

|

||||||

|

* This file is subject to the terms and conditions of the GNU Lesser

|

||||||

|

* General Public License v2.1. See the file LICENSE in the top level

|

||||||

|

* directory for more details.

|

||||||

|

*/

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @ingroup boards_common_saml1x

|

||||||

|

* @{

|

||||||

|

*

|

||||||

|

* @file board.c

|

||||||

|

* @brief Board specific implementations for the Microchip

|

||||||

|

* SAML10 and SAML11 Xplained Pro board

|

||||||

|

*

|

||||||

|

* @author Dylan Laduranty <dylan.laduranty@mesotic.com>

|

||||||

|

*

|

||||||

|

* @}

|

||||||

|

*/

|

||||||

|

|

||||||

|

#include "cpu.h"

|

||||||

|

#include "board.h"

|

||||||

|

#include "periph/gpio.h"

|

||||||

|

|

||||||

|

void led_init(void);

|

||||||

|

|

||||||

|

void board_init(void)

|

||||||

|

{

|

||||||

|

/* initialize the boards LEDs */

|

||||||

|

led_init();

|

||||||

|

/* initialize the CPU */

|

||||||

|

cpu_init();

|

||||||

|

|

||||||

|

}

|

||||||

|

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @brief Initialize the boards on-board LED

|

||||||

|

*/

|

||||||

|

void led_init(void)

|

||||||

|

{

|

||||||

|

gpio_init(GPIO_PIN(PA, 7), GPIO_OUT);

|

||||||

|

}

|

||||||

76

boards/common/saml1x/include/board.h

Normal file

76

boards/common/saml1x/include/board.h

Normal file

@ -0,0 +1,76 @@

|

|||||||

|

/*

|

||||||

|

* Copyright (C) 2019 Mesotic SAS

|

||||||

|

*

|

||||||

|

* This file is subject to the terms and conditions of the GNU Lesser

|

||||||

|

* General Public License v2.1. See the file LICENSE in the top level

|

||||||

|

* directory for more details.

|

||||||

|

*/

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @defgroup boards_common_saml1x Microchip SAML1X

|

||||||

|

* @ingroup boards

|

||||||

|

* @brief Support for SAML10 and SAML11 boards

|

||||||

|

* @{

|

||||||

|

*

|

||||||

|

* @file

|

||||||

|

* @brief Board specific definitions for the Microchip

|

||||||

|

* SAML10 & SAML11 Xplained Pro board.

|

||||||

|

*

|

||||||

|

* @author Dylan Laduranty <dylan.laduranty@mesotic.com>

|

||||||

|

*/

|

||||||

|

|

||||||

|

#ifndef BOARD_H

|

||||||

|

#define BOARD_H

|

||||||

|

|

||||||

|

#include "cpu.h"

|

||||||

|

|

||||||

|

#ifdef __cplusplus

|

||||||

|

extern "C" {

|

||||||

|

#endif

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name PORT selection macros

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

#ifdef CPU_FAM_SAML11

|

||||||

|

#define _PORT PORT_SEC

|

||||||

|

#else

|

||||||

|

#define _PORT PORT

|

||||||

|

#endif

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name LED pin definitions and handlers

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

#define LED0_PIN GPIO_PIN(PA, 7)

|

||||||

|

|

||||||

|

#define LED_PORT _PORT->Group[PA]

|

||||||

|

#define LED0_MASK (1 << 7)

|

||||||

|

|

||||||

|

#define LED0_ON (LED_PORT.OUTCLR.reg = LED0_MASK)

|

||||||

|

#define LED0_OFF (LED_PORT.OUTSET.reg = LED0_MASK)

|

||||||

|

#define LED0_TOGGLE (LED_PORT.OUTTGL.reg = LED0_MASK)

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name SW0 (Button) pin definitions

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

#define BTN0_PORT _PORT->Group[PA]

|

||||||

|

#define BTN0_PIN GPIO_PIN(PA, 27)

|

||||||

|

#define BTN0_MODE GPIO_IN_PU

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @brief Initialize board specific hardware, including clock, LEDs and std-IO

|

||||||

|

*/

|

||||||

|

void board_init(void);

|

||||||

|

|

||||||

|

#ifdef __cplusplus

|

||||||

|

}

|

||||||

|

#endif

|

||||||

|

|

||||||

|

#endif /* BOARD_H */

|

||||||

|

/** @} */

|

||||||

53

boards/common/saml1x/include/gpio_params.h

Normal file

53

boards/common/saml1x/include/gpio_params.h

Normal file

@ -0,0 +1,53 @@

|

|||||||

|

/*

|

||||||

|

* Copyright (C) 2019 Mesotic SAS

|

||||||

|

*

|

||||||

|

* This file is subject to the terms and conditions of the GNU Lesser

|

||||||

|

* General Public License v2.1. See the file LICENSE in the top level

|

||||||

|

* directory for more details.

|

||||||

|

*/

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @ingroup boards_common_saml1x

|

||||||

|

* @{

|

||||||

|

*

|

||||||

|

* @file

|

||||||

|

* @brief Board specific configuration of direct mapped GPIOs

|

||||||

|

*

|

||||||

|

* @author Dylan Laduranty <dylan.laduranty@mesotic.com>

|

||||||

|

*/

|

||||||

|

|

||||||

|

#ifndef GPIO_PARAMS_H

|

||||||

|

#define GPIO_PARAMS_H

|

||||||

|

|

||||||

|

#include "board.h"

|

||||||

|

#include "saul/periph.h"

|

||||||

|

|

||||||

|

#ifdef __cplusplus

|

||||||

|

extern "C" {

|

||||||

|

#endif

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @brief GPIO pin configuration

|

||||||

|

*/

|

||||||

|

static const saul_gpio_params_t saul_gpio_params[] =

|

||||||

|

{

|

||||||

|

{

|

||||||

|

.name = "LED(orange)",

|

||||||

|

.pin = LED0_PIN,

|

||||||

|

.mode = GPIO_OUT,

|

||||||

|

.flags = (SAUL_GPIO_INVERTED | SAUL_GPIO_INIT_CLEAR)

|

||||||

|

},

|

||||||

|

{

|

||||||

|

.name = "Button(SW0)",

|

||||||

|

.pin = BTN0_PIN,

|

||||||

|

.mode = BTN0_MODE,

|

||||||

|

.flags = SAUL_GPIO_INVERTED

|

||||||

|

},

|

||||||

|

};

|

||||||

|

|

||||||

|

#ifdef __cplusplus

|

||||||

|

}

|

||||||

|

#endif

|

||||||

|

|

||||||

|

#endif /* GPIO_PARAMS_H */

|

||||||

|

/** @} */

|

||||||

155

boards/common/saml1x/include/periph_conf.h

Normal file

155

boards/common/saml1x/include/periph_conf.h

Normal file

@ -0,0 +1,155 @@

|

|||||||

|

/*

|

||||||

|

* Copyright (C) 2019 Mesotic SAS

|

||||||

|

*

|

||||||

|

* This file is subject to the terms and conditions of the GNU Lesser

|

||||||

|

* General Public License v2.1. See the file LICENSE in the top level

|

||||||

|

* directory for more details.

|

||||||

|

*/

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @ingroup boards_common_saml1x

|

||||||

|

* @{

|

||||||

|

*

|

||||||

|

* @file

|

||||||

|

* @brief Peripheral MCU configuration for the Microchip

|

||||||

|

* SAML10 & SAML11 Xplained Pro board

|

||||||

|

*

|

||||||

|

* @author Dylan Laduranty <dylan.laduranty@mesotic.com>

|

||||||

|

*/

|

||||||

|

|

||||||

|

#ifndef PERIPH_CONF_H

|

||||||

|

#define PERIPH_CONF_H

|

||||||

|

|

||||||

|

#include "periph_cpu.h"

|

||||||

|

|

||||||

|

#ifdef __cplusplus

|

||||||

|

extern "C" {

|

||||||

|

#endif

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @brief GCLK reference speed

|

||||||

|

*/

|

||||||

|

#define CLOCK_CORECLOCK (16000000U)

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name Timer peripheral configuration

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

#define TIMER_NUMOF (1U)

|

||||||

|

#define TIMER_0_EN 1

|

||||||

|

|

||||||

|

/* Timer 0 configuration */

|

||||||

|

#define TIMER_0_DEV TC0->COUNT32

|

||||||

|

#define TIMER_0_CHANNELS 1

|

||||||

|

#define TIMER_0_MAX_VALUE (0xffffffff)

|

||||||

|

#define TIMER_0_ISR isr_tc0

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name UART configuration

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

static const uart_conf_t uart_config[] = {

|

||||||

|

{ /* Virtual COM Port */

|

||||||

|

.dev = &SERCOM2->USART,

|

||||||

|

.rx_pin = GPIO_PIN(PA,25),

|

||||||

|

.tx_pin = GPIO_PIN(PA,24),

|

||||||

|

.mux = GPIO_MUX_D,

|

||||||

|

.rx_pad = UART_PAD_RX_3,

|

||||||

|

.tx_pad = UART_PAD_TX_2,

|

||||||

|

.flags = UART_FLAG_NONE,

|

||||||

|

.gclk_src = GCLK_PCHCTRL_GEN_GCLK0

|

||||||

|

}

|

||||||

|

};

|

||||||

|

|

||||||

|

/* interrupt function name mapping */

|

||||||

|

#define UART_0_ISR isr_sercom2_2

|

||||||

|

|

||||||

|

#define UART_NUMOF (sizeof(uart_config) / sizeof(uart_config[0]))

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name SPI configuration

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

static const spi_conf_t spi_config[] = {

|

||||||

|

{

|

||||||

|

.dev = &(SERCOM0->SPI),

|

||||||

|

.miso_pin = GPIO_PIN(PA, 4),

|

||||||

|

.mosi_pin = GPIO_PIN(PA, 14),

|

||||||

|

.clk_pin = GPIO_PIN(PA, 15),

|

||||||

|

.miso_mux = GPIO_MUX_D,

|

||||||

|

.mosi_mux = GPIO_MUX_D,

|

||||||

|

.clk_mux = GPIO_MUX_D,

|

||||||

|

.miso_pad = SPI_PAD_MISO_0,

|

||||||

|

.mosi_pad = SPI_PAD_MOSI_2_SCK_3

|

||||||

|

|

||||||

|

}

|

||||||

|

};

|

||||||

|

|

||||||

|

#define SPI_NUMOF (sizeof(spi_config) / sizeof(spi_config[0]))

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name I2C configuration

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

static const i2c_conf_t i2c_config[] = {

|

||||||

|

{

|

||||||

|

.dev = &(SERCOM1->I2CM),

|

||||||

|

.speed = I2C_SPEED_NORMAL,

|

||||||

|

.scl_pin = GPIO_PIN(PA, 17),

|

||||||

|

.sda_pin = GPIO_PIN(PA, 16),

|

||||||

|

.mux = GPIO_MUX_C,

|

||||||

|

.gclk_src = GCLK_PCHCTRL_GEN_GCLK0,

|

||||||

|

.flags = I2C_FLAG_NONE

|

||||||

|

}

|

||||||

|

};

|

||||||

|

|

||||||

|

#define I2C_NUMOF (sizeof(i2c_config) / sizeof(i2c_config[0]))

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name RTC configuration

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

#define RTC_NUMOF (1)

|

||||||

|

#define EXTERNAL_OSC32_SOURCE 1

|

||||||

|

#define INTERNAL_OSC32_SOURCE 0

|

||||||

|

#define ULTRA_LOW_POWER_INTERNAL_OSC_SOURCE 0

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name RTT configuration

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

#define RTT_FREQUENCY (32768U)

|

||||||

|

#define RTT_MAX_VALUE (0xffffffffU)

|

||||||

|

#define RTT_NUMOF (1)

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @name ADC Configuration

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

#define ADC_NUMOF (1U)

|

||||||

|

|

||||||

|

/* ADC 0 Default values */

|

||||||

|

#define ADC_0_CLK_SOURCE 0 /* GCLK_GENERATOR_0 */

|

||||||

|

#define ADC_0_PRESCALER ADC_CTRLB_PRESCALER_DIV256

|

||||||

|

|

||||||

|

static const adc_conf_chan_t adc_channels[] = {

|

||||||

|

/* port, pin, muxpos */

|

||||||

|

{GPIO_PIN(PA, 10), ADC_INPUTCTRL_MUXPOS(ADC_INPUTCTRL_MUXPOS_AIN8)},

|

||||||

|

};

|

||||||

|

|

||||||

|

#define ADC_0_NEG_INPUT ADC_INPUTCTRL_MUXNEG(0x18u)

|

||||||

|

#define ADC_0_REF_DEFAULT ADC_REFCTRL_REFSEL_INTVCC2

|

||||||

|

/** @} */

|

||||||

|

|

||||||

|

#ifdef __cplusplus

|

||||||

|

}

|

||||||

|

#endif

|

||||||

|

|

||||||

|

#endif /* PERIPH_CONF_H */

|

||||||

|

/** @} */

|

||||||

4

boards/saml10-xpro/Makefile

Normal file

4

boards/saml10-xpro/Makefile

Normal file

@ -0,0 +1,4 @@

|

|||||||

|

MODULE = board

|

||||||

|

DIRS = $(RIOTBOARD)/common/saml1x

|

||||||

|

|

||||||

|

include $(RIOTBASE)/Makefile.base

|

||||||

1

boards/saml10-xpro/Makefile.dep

Normal file

1

boards/saml10-xpro/Makefile.dep

Normal file

@ -0,0 +1 @@

|

|||||||

|

include $(RIOTBOARD)/common/saml1x/Makefile.dep

|

||||||

1

boards/saml10-xpro/Makefile.features

Normal file

1

boards/saml10-xpro/Makefile.features

Normal file

@ -0,0 +1 @@

|

|||||||

|

include $(RIOTBOARD)/common/saml1x/Makefile.features

|

||||||

5

boards/saml10-xpro/Makefile.include

Normal file

5

boards/saml10-xpro/Makefile.include

Normal file

@ -0,0 +1,5 @@

|

|||||||

|

export CPU_FAM = saml10

|

||||||

|

export CPU_MODEL = saml10e16a

|

||||||

|

export CFLAGS += -D__SAML10E16A__

|

||||||

|

|

||||||

|

include $(RIOTBOARD)/common/saml1x/Makefile.include

|

||||||

75

boards/saml10-xpro/doc.txt

Normal file

75

boards/saml10-xpro/doc.txt

Normal file

@ -0,0 +1,75 @@

|

|||||||

|

/**

|

||||||

|

@defgroup boards_saml10-xpro Microchip SAML10 Xplained Pro

|

||||||

|

@ingroup boards

|

||||||

|

@brief Support for the Microchip SAML10 Xplained Pro board.

|

||||||

|

|

||||||

|

## Overview

|

||||||

|

|

||||||

|

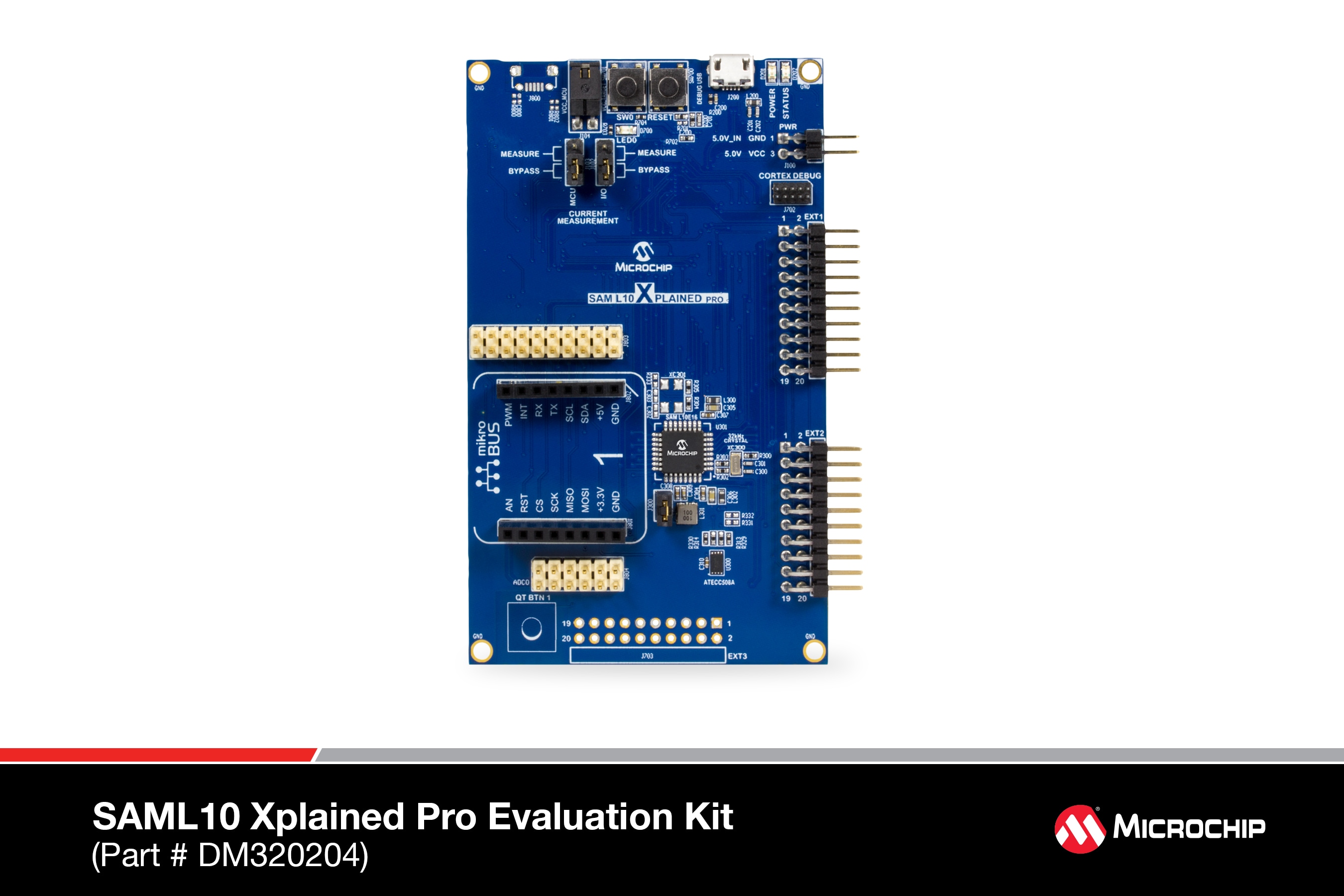

The `SAML10 Xplained Pro` is an ultra-low power evaluation board by Microchip

|

||||||

|

featuring a ATSAML10E16A SoC. The SoC includes a SAML10 ARM Cortex-M23 micro-

|

||||||

|

controller. For programming the MCU comes with 16KB of RAM and 64KB of flash

|

||||||

|

memory.

|

||||||

|

|

||||||

|

## Hardware

|

||||||

|

|

||||||

|

|

||||||

|

|

||||||

|

|

||||||

|

### MCU

|

||||||

|

| MCU | ATSAML10E16A |

|

||||||

|

|:------------- |:--------------------- |

|

||||||

|

| Family | ARM Cortex-M23 |

|

||||||

|

| Vendor | Microchip |

|

||||||

|

| RAM | 16KB |

|

||||||

|

| Flash | 64KB |

|

||||||

|

| Frequency | up to 32MHz |

|

||||||

|

| FPU | no |

|

||||||

|

| Timers | 3 (16-bit) |

|

||||||

|

| ADCs | 1x 12-bit (10 channels) |

|

||||||

|

| UARTs | max 3 (shared with SPI and I2C) |

|

||||||

|

| SPIs | max 3 (see UART) |

|

||||||

|

| I2Cs | max 3 (see UART) |

|

||||||

|

| Vcc | 1.6V - 3.6V |

|

||||||

|

| Datasheet | [Datasheet](http://ww1.microchip.com/downloads/en/DeviceDoc/SAM-L10L11%20Family-DataSheet%20-%20DS60001513B.pdf) |

|

||||||

|

| Board Manual | [Board Manual](http://ww1.microchip.com/downloads/en/DeviceDoc/70005359B.pdf)|

|

||||||

|

|

||||||

|

### User Interface

|

||||||

|

|

||||||

|

1 User button and 1 LED:

|

||||||

|

|

||||||

|

| Device | PIN |

|

||||||

|

|:------ |:--- |

|

||||||

|

| LED0 | PA07 |

|

||||||

|

| SW0 (button) | PA27 |

|

||||||

|

|

||||||

|

|

||||||

|

## Implementation Status

|

||||||

|

|

||||||

|

| Device | ID | Supported | Comments |

|

||||||

|

|:------------- |:------------- |:------------- |:------------- |

|

||||||

|

| MCU | saml10 | partly | PLL clock not implemented |

|

||||||

|

| Low-level driver | GPIO | yes | |

|

||||||

|

| | PWM | no | |

|

||||||

|

| | UART | yes | |

|

||||||

|

| | I2C | no | |

|

||||||

|

| | SPI | no | |

|

||||||

|

| | USB | no | |

|

||||||

|

| | RTT | no | |

|

||||||

|

| | RTC | no | |

|

||||||

|

| | RNG | no | |

|

||||||

|

| | Timer | yes | |

|

||||||

|

| | ADC | no | |

|

||||||

|

|

||||||

|

## Flashing the device

|

||||||

|

|

||||||

|

Connect the device to your Micro-USB cable.

|

||||||

|

|

||||||

|

The standard method for flashing RIOT to the saml10-xpro is using EDBG.

|

||||||

|

|

||||||

|

## Supported Toolchains

|

||||||

|

|

||||||

|

For using the saml10-xpro board we strongly recommend the usage of the

|

||||||

|

[GNU Tools for ARM Embedded Processors](https://launchpad.net/gcc-arm-embedded)

|

||||||

|

toolchain.

|

||||||

|

|

||||||

|

*/

|

||||||

4

boards/saml11-xpro/Makefile

Normal file

4

boards/saml11-xpro/Makefile

Normal file

@ -0,0 +1,4 @@

|

|||||||

|

MODULE = board

|

||||||

|

DIRS = $(RIOTBOARD)/common/saml1x

|

||||||

|

|

||||||

|

include $(RIOTBASE)/Makefile.base

|

||||||

1

boards/saml11-xpro/Makefile.dep

Normal file

1

boards/saml11-xpro/Makefile.dep

Normal file

@ -0,0 +1 @@

|

|||||||

|

include $(RIOTBOARD)/common/saml1x/Makefile.dep

|

||||||

1

boards/saml11-xpro/Makefile.features

Normal file

1

boards/saml11-xpro/Makefile.features

Normal file

@ -0,0 +1 @@

|

|||||||

|

include $(RIOTBOARD)/common/saml1x/Makefile.features

|

||||||

5

boards/saml11-xpro/Makefile.include

Normal file

5

boards/saml11-xpro/Makefile.include

Normal file

@ -0,0 +1,5 @@

|

|||||||

|

export CPU_FAM = saml11

|

||||||

|

export CPU_MODEL = saml11e16a

|

||||||

|

export CFLAGS += -D__SAML11E16A__

|

||||||

|

|

||||||

|

include $(RIOTBOARD)/common/saml1x/Makefile.include

|

||||||

77

boards/saml11-xpro/doc.txt

Normal file

77

boards/saml11-xpro/doc.txt

Normal file

@ -0,0 +1,77 @@

|

|||||||

|

/**

|

||||||

|

@defgroup boards_saml11-xpro Microchip SAML11 Xplained Pro

|

||||||

|

@ingroup boards

|

||||||

|

@brief Support for the Microchip SAML11 Xplained Pro board.

|

||||||

|

|

||||||

|

## Overview

|

||||||

|

|

||||||

|

The `SAML11 Xplained Pro` is an ultra-low power evaluation board by Microchip

|

||||||

|

featuring a ATSAML11E16A SoC. The SoC includes a SAML11 ARM Cortex-M23 micro-

|

||||||

|

controller. For programming the MCU comes with 16KB of RAM and 64KB of flash

|

||||||

|

memory. In addition, this SoC features the ARM TrustZone technology.

|

||||||

|

|

||||||

|

## Hardware

|

||||||

|

|

||||||

|

|

||||||

|

|

||||||

|

|

||||||

|

### MCU

|

||||||

|

| MCU | ATSAML11E14A |

|

||||||

|

|:------------- |:--------------------- |

|

||||||

|

| Family | ARM Cortex-M23 |

|

||||||

|

| Vendor | Microchip |

|

||||||

|

| RAM | 16KB |

|

||||||

|

| Flash | 64KB |

|

||||||

|

| Frequency | up to 32MHz |

|

||||||

|

| FPU | no |

|

||||||

|

| Timers | 3 (16-bit) |

|

||||||

|

| ADCs | 1x 12-bit (10 channels) |

|

||||||

|

| UARTs | max 3 (shared with SPI and I2C) |

|

||||||

|

| SPIs | max 3 (see UART) |

|

||||||

|

| I2Cs | max 3 (see UART) |

|

||||||

|

| Vcc | 1.6V - 3.6V |

|

||||||

|

| Datasheet | [Datasheet](http://ww1.microchip.com/downloads/en/DeviceDoc/SAM-L10L11%20Family-DataSheet%20-%20DS60001513B.pdf) |

|

||||||

|

| Board Manual | [Board Manual](http://ww1.microchip.com/downloads/en/DeviceDoc/70005359B.pdf)|

|

||||||

|

|

||||||

|

### User Interface

|

||||||

|

|

||||||

|

1 User button and 1 LED:

|

||||||

|

|

||||||

|

| Device | PIN |

|

||||||

|

|:------ |:--- |

|

||||||

|

| LED0 | PA07 |

|

||||||

|

| SW0 (button) | PA27 |

|

||||||

|

|

||||||

|

|

||||||

|

## Implementation Status

|

||||||

|

|

||||||

|

| Device | ID | Supported | Comments |

|

||||||

|

|:------------- |:------------- |:------------- |:------------- |

|

||||||

|

| MCU | saml11 | partly | PLL clock not implemented |

|

||||||

|

| Low-level driver | GPIO | yes | |

|

||||||

|

| | PWM | no | |

|

||||||

|

| | UART | yes | |

|

||||||

|

| | I2C | no | |

|

||||||

|

| | SPI | no | |

|

||||||

|

| | USB | no | |

|

||||||

|

| | RTT | no | |

|

||||||

|

| | RTC | no | |

|

||||||

|

| | RNG | no | |

|

||||||

|

| | Timer | yes | |

|

||||||

|

| | ADC | no | |

|

||||||

|

|

||||||

|

|

||||||

|

|

||||||

|

## Flashing the device

|

||||||

|

|

||||||

|

Connect the device to your Micro-USB cable.

|

||||||

|

|

||||||

|

The standard method for flashing RIOT to the saml11-xpro is using EDBG.

|

||||||

|

|

||||||

|

## Supported Toolchains

|

||||||

|

|

||||||

|

For using the saml11-xpro board we strongly recommend the usage of the

|

||||||

|

[GNU Tools for ARM Embedded Processors](https://launchpad.net/gcc-arm-embedded)

|

||||||

|

toolchain.

|

||||||

|

|

||||||

|

*/

|

||||||

@ -65,7 +65,8 @@ void cortexm_init(void)

|

|||||||

/* configure the vector table location to internal flash */

|

/* configure the vector table location to internal flash */

|

||||||

#if defined(CPU_ARCH_CORTEX_M3) || defined(CPU_ARCH_CORTEX_M4) || \

|

#if defined(CPU_ARCH_CORTEX_M3) || defined(CPU_ARCH_CORTEX_M4) || \

|

||||||

defined(CPU_ARCH_CORTEX_M4F) || defined(CPU_ARCH_CORTEX_M7) || \

|

defined(CPU_ARCH_CORTEX_M4F) || defined(CPU_ARCH_CORTEX_M7) || \

|

||||||

(defined(CPU_ARCH_CORTEX_M0PLUS) && (__VTOR_PRESENT == 1))

|

(defined(CPU_ARCH_CORTEX_M0PLUS) || defined(CPU_ARCH_CORTEX_M23) \

|

||||||

|

&& (__VTOR_PRESENT == 1))

|

||||||

SCB->VTOR = (uint32_t)&_isr_vectors;

|

SCB->VTOR = (uint32_t)&_isr_vectors;

|

||||||

#endif

|

#endif

|

||||||

|

|

||||||

|

|||||||

@ -59,7 +59,8 @@ bool mpu_enabled(void) {

|

|||||||

}

|

}

|

||||||

|

|

||||||

int mpu_configure(uint_fast8_t region, uintptr_t base, uint_fast32_t attr) {

|

int mpu_configure(uint_fast8_t region, uintptr_t base, uint_fast32_t attr) {

|

||||||

#if __MPU_PRESENT

|

/* Todo enable MPU support for Cortex-M23/M33 */

|

||||||

|

#if __MPU_PRESENT && !defined(CPU_ARCH_CORTEX_M23)

|

||||||

assert(region < MPU_NUM_REGIONS);

|

assert(region < MPU_NUM_REGIONS);

|

||||||

|

|

||||||

MPU->RNR = region;

|

MPU->RNR = region;

|

||||||

|

|||||||

@ -187,7 +187,8 @@ char *thread_stack_init(thread_task_func_t task_func,

|

|||||||

* For the Cortex-M3 and Cortex-M4 we write them continuously onto the stack

|

* For the Cortex-M3 and Cortex-M4 we write them continuously onto the stack

|

||||||

* as they can be read/written continuously by stack instructions. */

|

* as they can be read/written continuously by stack instructions. */

|

||||||

|

|

||||||

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS)

|

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS) \

|

||||||

|

|| defined(CPU_ARCH_CORTEX_M23)

|

||||||

/* start with r7 - r4 */

|

/* start with r7 - r4 */

|

||||||

for (int i = 7; i >= 4; i--) {

|

for (int i = 7; i >= 4; i--) {

|

||||||

stk--;

|

stk--;

|

||||||

@ -286,7 +287,8 @@ void __attribute__((naked)) __attribute__((used)) isr_pendsv(void) {

|

|||||||

/* {r0-r3,r12,LR,PC,xPSR,s0-s15,FPSCR} are saved automatically on exception entry */

|

/* {r0-r3,r12,LR,PC,xPSR,s0-s15,FPSCR} are saved automatically on exception entry */

|

||||||

".thumb_func \n"

|

".thumb_func \n"

|

||||||

"mrs r0, psp \n" /* get stack pointer from user mode */

|

"mrs r0, psp \n" /* get stack pointer from user mode */

|

||||||

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS)

|

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS) \

|

||||||

|

|| defined(CPU_ARCH_CORTEX_M23)

|

||||||

"mov r12, sp \n" /* remember the exception SP */

|

"mov r12, sp \n" /* remember the exception SP */

|

||||||

"mov sp, r0 \n" /* set user mode SP as active SP */

|

"mov sp, r0 \n" /* set user mode SP as active SP */

|

||||||

/* we can not push high registers directly, so we move R11-R8 into

|

/* we can not push high registers directly, so we move R11-R8 into

|

||||||

@ -326,7 +328,8 @@ void __attribute__((naked)) __attribute__((used)) isr_svc(void) {

|

|||||||

/* restore context and return from exception */

|

/* restore context and return from exception */

|

||||||

".thumb_func \n"

|

".thumb_func \n"

|

||||||

"context_restore: \n"

|

"context_restore: \n"

|

||||||

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS)

|

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS) \

|

||||||

|

|| defined(CPU_ARCH_CORTEX_M23)

|

||||||

"mov lr, sp \n" /* save MSR stack pointer for later */

|

"mov lr, sp \n" /* save MSR stack pointer for later */

|

||||||

"ldr r0, =sched_active_thread \n" /* load address of current TCB */

|

"ldr r0, =sched_active_thread \n" /* load address of current TCB */

|

||||||

"ldr r0, [r0] \n" /* dereference TCB */

|

"ldr r0, [r0] \n" /* dereference TCB */

|

||||||

|

|||||||

@ -188,7 +188,8 @@ __attribute__((naked)) void hard_fault_default(void)

|

|||||||

" use_psp: \n" /* else { */

|

" use_psp: \n" /* else { */

|

||||||

"mrs r0, psp \n" /* r0 = psp */

|

"mrs r0, psp \n" /* r0 = psp */

|

||||||

" out: \n" /* } */

|

" out: \n" /* } */

|

||||||

#if (__CORTEX_M == 0)

|

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS) \

|

||||||

|

|| defined(CPU_ARCH_CORTEX_M23)

|

||||||

"push {r4-r7} \n" /* save r4..r7 to the stack */

|

"push {r4-r7} \n" /* save r4..r7 to the stack */

|

||||||

"mov r3, r8 \n" /* */

|

"mov r3, r8 \n" /* */

|

||||||

"mov r4, r9 \n" /* */

|

"mov r4, r9 \n" /* */

|

||||||

@ -208,9 +209,10 @@ __attribute__((naked)) void hard_fault_default(void)

|

|||||||

);

|

);

|

||||||

}

|

}

|

||||||

|

|

||||||

#if (__CORTEX_M == 0)

|

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS) \

|

||||||

/* Cortex-M0 and Cortex-M0+ lack the extended fault status registers found in

|

|| defined(CPU_ARCH_CORTEX_M23)

|

||||||

* Cortex-M3 and above. */

|

/* Cortex-M0, Cortex-M0+ and Cortex-M23 lack the extended fault status

|

||||||

|

registers found in Cortex-M3 and above. */

|

||||||

#define CPU_HAS_EXTENDED_FAULT_REGISTERS 0

|

#define CPU_HAS_EXTENDED_FAULT_REGISTERS 0

|

||||||

#else

|

#else

|

||||||

#define CPU_HAS_EXTENDED_FAULT_REGISTERS 1

|

#define CPU_HAS_EXTENDED_FAULT_REGISTERS 1

|

||||||

@ -261,11 +263,12 @@ __attribute__((used)) void hard_fault_handler(uint32_t* sp, uint32_t corrupted,

|

|||||||

|

|

||||||

/* Reconstruct original stack pointer before fault occurred */

|

/* Reconstruct original stack pointer before fault occurred */

|

||||||

orig_sp = sp + 8;

|

orig_sp = sp + 8;

|

||||||

|

#ifdef SCB_CCR_STKALIGN_Msk

|

||||||

if (psr & SCB_CCR_STKALIGN_Msk) {

|

if (psr & SCB_CCR_STKALIGN_Msk) {

|

||||||

/* Stack was not 8-byte aligned */

|

/* Stack was not 8-byte aligned */

|

||||||

orig_sp += 1;

|

orig_sp += 1;

|

||||||

}

|

}

|

||||||

|

#endif /* SCB_CCR_STKALIGN_Msk */

|

||||||

puts("\nContext before hardfault:");

|

puts("\nContext before hardfault:");

|

||||||

|

|

||||||

/* TODO: printf in ISR context might be a bad idea */

|

/* TODO: printf in ISR context might be a bad idea */

|

||||||

@ -315,7 +318,8 @@ __attribute__((used)) void hard_fault_handler(uint32_t* sp, uint32_t corrupted,

|

|||||||

"mov lr, r1\n"

|

"mov lr, r1\n"

|

||||||

"mov sp, %[orig_sp]\n"

|

"mov sp, %[orig_sp]\n"

|

||||||

"mov r1, %[extra_stack]\n"

|

"mov r1, %[extra_stack]\n"

|

||||||

#if (__CORTEX_M == 0)

|

#if defined(CPU_ARCH_CORTEX_M0) || defined(CPU_ARCH_CORTEX_M0PLUS) \

|

||||||

|

|| defined(CPU_ARCH_CORTEX_M23)

|

||||||

"ldm r1!, {r4-r7}\n"

|

"ldm r1!, {r4-r7}\n"

|

||||||

"mov r8, r4\n"

|

"mov r8, r4\n"

|

||||||

"mov r9, r5\n"

|

"mov r9, r5\n"

|

||||||

|

|||||||

@ -6,12 +6,18 @@ ifneq (,$(filter samd21g18a samd21j18a saml21j18b saml21j18a samr21g18a samr30g1

|

|||||||

ROM_LEN ?= 0x40000

|

ROM_LEN ?= 0x40000

|

||||||

RAM_LEN ?= 0x8000

|

RAM_LEN ?= 0x8000

|

||||||

endif

|

endif

|

||||||

|

ifneq (,$(filter saml10e16a saml11e16a,$(CPU_MODEL)))

|

||||||

|

ROM_LEN ?= 64K

|

||||||

|

RAM_LEN ?= 16K

|

||||||

|

endif

|

||||||

|

|

||||||

ROM_START_ADDR ?= 0x00000000

|

ROM_START_ADDR ?= 0x00000000

|

||||||

RAM_START_ADDR ?= 0x20000000

|

RAM_START_ADDR ?= 0x20000000

|

||||||

|

|

||||||

# this CPU implementation doesn't use CMSIS initialization

|

# this CPU implementation doesn't use CMSIS initialization

|

||||||

export CFLAGS += -DDONT_USE_CMSIS_INIT

|

export CFLAGS += -DDONT_USE_CMSIS_INIT

|

||||||

|

export CFLAGS += -DDONT_USE_PREDEFINED_CORE_HANDLERS

|

||||||

|

export CFLAGS += -DDONT_USE_PREDEFINED_PERIPHERALS_HANDLERS

|

||||||

|

|

||||||

# For Cortex-M cpu we use the common cortexm.ld linker script

|

# For Cortex-M cpu we use the common cortexm.ld linker script

|

||||||

LINKER_SCRIPT ?= cortexm.ld

|

LINKER_SCRIPT ?= cortexm.ld

|

||||||

|

|||||||

@ -22,7 +22,11 @@

|

|||||||

#define CPU_CONF_H

|

#define CPU_CONF_H

|

||||||

|

|

||||||

#include "cpu_conf_common.h"

|

#include "cpu_conf_common.h"

|

||||||

|

#if defined(CPU_SAML1X)

|

||||||

|

#include "vendor/sam23.h"

|

||||||

|

#else

|

||||||

#include "vendor/sam0.h"

|

#include "vendor/sam0.h"

|

||||||

|

#endif

|

||||||

|

|

||||||

#ifdef __cplusplus

|

#ifdef __cplusplus

|

||||||

extern "C" {

|

extern "C" {

|

||||||

|

|||||||

@ -69,7 +69,11 @@ typedef uint32_t gpio_t;

|

|||||||

* @brief Macro for accessing GPIO pins

|

* @brief Macro for accessing GPIO pins

|

||||||

* @{

|

* @{

|

||||||

*/

|

*/

|

||||||

|

#ifdef CPU_FAM_SAML11

|

||||||

|

#define GPIO_PIN(x, y) (((gpio_t)(&PORT_SEC->Group[x])) | y)

|

||||||

|

#else

|

||||||

#define GPIO_PIN(x, y) (((gpio_t)(&PORT->Group[x])) | y)

|

#define GPIO_PIN(x, y) (((gpio_t)(&PORT->Group[x])) | y)

|

||||||

|

#endif

|

||||||

|

|

||||||

/**

|

/**

|

||||||

* @brief Available ports on the SAMD21 & SAML21

|

* @brief Available ports on the SAMD21 & SAML21

|

||||||

@ -94,7 +98,11 @@ enum {

|

|||||||

* @name Power mode configuration

|

* @name Power mode configuration

|

||||||

* @{

|

* @{

|

||||||

*/

|

*/

|

||||||

|

#ifdef CPU_FAM_SAML11

|

||||||

|

#define PM_NUM_MODES (2)

|

||||||

|

#else

|

||||||

#define PM_NUM_MODES (3)

|

#define PM_NUM_MODES (3)

|

||||||

|

#endif

|

||||||

/** @} */

|

/** @} */

|

||||||

|

|

||||||

#ifndef DOXYGEN

|

#ifndef DOXYGEN

|

||||||

@ -127,6 +135,7 @@ typedef enum {

|

|||||||

/**

|

/**

|

||||||

* @brief Available MUX values for configuring a pin's alternate function

|

* @brief Available MUX values for configuring a pin's alternate function

|

||||||

*/

|

*/

|

||||||

|

#ifndef SAM_MUX_T

|

||||||

typedef enum {

|

typedef enum {

|

||||||

GPIO_MUX_A = 0x0, /**< select peripheral function A */

|

GPIO_MUX_A = 0x0, /**< select peripheral function A */

|

||||||

GPIO_MUX_B = 0x1, /**< select peripheral function B */

|

GPIO_MUX_B = 0x1, /**< select peripheral function B */

|

||||||

@ -137,6 +146,7 @@ typedef enum {

|

|||||||

GPIO_MUX_G = 0x6, /**< select peripheral function G */

|

GPIO_MUX_G = 0x6, /**< select peripheral function G */

|

||||||

GPIO_MUX_H = 0x7, /**< select peripheral function H */

|

GPIO_MUX_H = 0x7, /**< select peripheral function H */

|

||||||

} gpio_mux_t;

|

} gpio_mux_t;

|

||||||

|

#endif

|

||||||

|

|

||||||

/**

|

/**

|

||||||

* @brief Available values for SERCOM UART RX pad selection

|

* @brief Available values for SERCOM UART RX pad selection

|

||||||

@ -298,6 +308,8 @@ static inline int sercom_id(void *sercom)

|

|||||||

{

|

{

|

||||||

#if defined(CPU_FAM_SAMD21)

|

#if defined(CPU_FAM_SAMD21)

|

||||||

return ((((uint32_t)sercom) >> 10) & 0x7) - 2;

|

return ((((uint32_t)sercom) >> 10) & 0x7) - 2;

|

||||||

|

#elif defined (CPU_FAM_SAML10) || defined (CPU_FAM_SAML11)

|

||||||

|

return ((((uint32_t)sercom) >> 10) & 0x7) - 1;

|

||||||

#elif defined(CPU_FAM_SAML21) || defined(CPU_FAM_SAMR30)

|

#elif defined(CPU_FAM_SAML21) || defined(CPU_FAM_SAMR30)

|

||||||

/* Left side handles SERCOM0-4 while right side handles unaligned address of SERCOM5 */

|

/* Left side handles SERCOM0-4 while right side handles unaligned address of SERCOM5 */

|

||||||

return ((((uint32_t)sercom) >> 10) & 0x7) + ((((uint32_t)sercom) >> 22) & 0x04);

|

return ((((uint32_t)sercom) >> 10) & 0x7) + ((((uint32_t)sercom) >> 22) & 0x04);

|

||||||

@ -313,12 +325,15 @@ static inline void sercom_clk_en(void *sercom)

|

|||||||

{

|

{

|

||||||

#if defined(CPU_FAM_SAMD21)

|

#if defined(CPU_FAM_SAMD21)

|

||||||

PM->APBCMASK.reg |= (PM_APBCMASK_SERCOM0 << sercom_id(sercom));

|

PM->APBCMASK.reg |= (PM_APBCMASK_SERCOM0 << sercom_id(sercom));

|

||||||

#elif defined(CPU_FAM_SAML21) || defined(CPU_FAM_SAMR30)

|

#else

|

||||||

if (sercom_id(sercom) < 5) {

|

if (sercom_id(sercom) < 5) {

|

||||||

MCLK->APBCMASK.reg |= (MCLK_APBCMASK_SERCOM0 << sercom_id(sercom));

|

MCLK->APBCMASK.reg |= (MCLK_APBCMASK_SERCOM0 << sercom_id(sercom));

|

||||||

} else {

|

}

|

||||||

|

#if defined(CPU_FAM_SAML21)

|

||||||

|

else {

|

||||||

MCLK->APBDMASK.reg |= (MCLK_APBDMASK_SERCOM5);

|

MCLK->APBDMASK.reg |= (MCLK_APBDMASK_SERCOM5);

|

||||||

}

|

}

|

||||||

|

#endif /* CPU_FAM_SAML21 */

|

||||||

#endif

|

#endif

|

||||||

}

|

}

|

||||||

|

|

||||||

@ -331,12 +346,15 @@ static inline void sercom_clk_dis(void *sercom)

|

|||||||

{

|

{

|

||||||

#if defined(CPU_FAM_SAMD21)

|

#if defined(CPU_FAM_SAMD21)

|

||||||

PM->APBCMASK.reg &= ~(PM_APBCMASK_SERCOM0 << sercom_id(sercom));

|

PM->APBCMASK.reg &= ~(PM_APBCMASK_SERCOM0 << sercom_id(sercom));

|

||||||

#elif defined(CPU_FAM_SAML21) || defined(CPU_FAM_SAMR30)

|

#else

|

||||||

if (sercom_id(sercom) < 5) {

|

if (sercom_id(sercom) < 5) {

|

||||||

MCLK->APBCMASK.reg &= ~(MCLK_APBCMASK_SERCOM0 << sercom_id(sercom));

|

MCLK->APBCMASK.reg &= ~(MCLK_APBCMASK_SERCOM0 << sercom_id(sercom));

|

||||||

} else {

|

}

|

||||||

|

#if defined (CPU_FAM_SAML21)

|

||||||

|

else {

|

||||||

MCLK->APBDMASK.reg &= ~(MCLK_APBDMASK_SERCOM5);

|

MCLK->APBDMASK.reg &= ~(MCLK_APBDMASK_SERCOM5);

|

||||||

}

|

}

|

||||||

|

#endif /* CPU_FAM_SAML21 */

|

||||||

#endif

|

#endif

|

||||||

}

|

}

|

||||||

|

|

||||||

@ -352,14 +370,17 @@ static inline void sercom_set_gen(void *sercom, uint32_t gclk)

|

|||||||

GCLK->CLKCTRL.reg = (GCLK_CLKCTRL_CLKEN | gclk |

|

GCLK->CLKCTRL.reg = (GCLK_CLKCTRL_CLKEN | gclk |

|

||||||

(SERCOM0_GCLK_ID_CORE + sercom_id(sercom)));

|

(SERCOM0_GCLK_ID_CORE + sercom_id(sercom)));

|

||||||

while (GCLK->STATUS.reg & GCLK_STATUS_SYNCBUSY) {}

|

while (GCLK->STATUS.reg & GCLK_STATUS_SYNCBUSY) {}

|

||||||

#elif defined(CPU_FAM_SAML21) || defined(CPU_FAM_SAMR30)

|

#else

|

||||||

if (sercom_id(sercom) < 5) {

|

if (sercom_id(sercom) < 5) {

|

||||||

GCLK->PCHCTRL[SERCOM0_GCLK_ID_CORE + sercom_id(sercom)].reg =

|

GCLK->PCHCTRL[SERCOM0_GCLK_ID_CORE + sercom_id(sercom)].reg =

|

||||||

(GCLK_PCHCTRL_CHEN | gclk);

|

(GCLK_PCHCTRL_CHEN | gclk);

|

||||||

} else {

|

}

|

||||||

|

#if defined(CPU_FAM_SAML21)

|

||||||

|

else {

|

||||||

GCLK->PCHCTRL[SERCOM5_GCLK_ID_CORE].reg =

|

GCLK->PCHCTRL[SERCOM5_GCLK_ID_CORE].reg =

|

||||||

(GCLK_PCHCTRL_CHEN | gclk);

|

(GCLK_PCHCTRL_CHEN | gclk);

|

||||||

}

|

}

|

||||||

|

#endif /* CPU_FAM_SAML21 */

|

||||||

#endif

|

#endif

|

||||||

}

|

}

|

||||||

|

|

||||||

|

|||||||

78

cpu/sam0_common/include/vendor/sam23.h

vendored

Normal file

78

cpu/sam0_common/include/vendor/sam23.h

vendored

Normal file

@ -0,0 +1,78 @@

|

|||||||

|

/*

|

||||||

|

* Copyright (C) 2018 Mesotic SAS

|

||||||

|

*

|

||||||

|

* This file is subject to the terms and conditions of the GNU Lesser

|

||||||

|

* General Public License v2.1. See the file LICENSE in the top level

|

||||||

|

* directory for more details.

|

||||||

|

*/

|

||||||

|

|

||||||

|

/**

|

||||||

|

* @ingroup cpu_saml1x

|

||||||

|

* @{

|

||||||

|

*

|

||||||

|

* @file

|

||||||

|

* @brief Wrapper include file for including the specific

|

||||||

|

* SAML10/SAML11 vendor header

|

||||||

|

*

|

||||||

|

* @author Dylan Laduranty <dylan.laduranty@mesotic.com>

|

||||||

|

*/

|

||||||

|

|

||||||

|

#ifndef SAM23_H

|

||||||

|

#define SAM23_H

|

||||||

|

|

||||||

|

#ifdef __cplusplus

|

||||||

|

extern "C" {

|

||||||

|

#endif

|

||||||

|

|

||||||

|

/* Workaround redefinition of LITTLE_ENDIAN macro (part1) */

|

||||||

|

#ifdef LITTLE_ENDIAN

|

||||||

|

#define __TMP_LITTLE_ENDIAN LITTLE_ENDIAN

|

||||||

|

#undef LITTLE_ENDIAN

|

||||||

|

#endif

|

||||||

|

|

||||||

|

#if defined(CPU_MODEL_SAML10D14A)

|

||||||

|

#include "vendor/saml10/include/saml10d14a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML10D15A)

|

||||||

|

#include "vendor/saml10/include/saml10d15a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML10D16A)

|

||||||

|

#include "vendor/saml10/include/saml10d16a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML10E14A)

|

||||||

|

#include "vendor/saml10/include/saml10e14a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML10E15A)

|

||||||

|

#include "vendor/saml10/include/saml10e15a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML10E16A)

|

||||||

|

#include "vendor/saml10/include/saml10e16a.h"

|

||||||

|

|

||||||

|

#elif defined(CPU_MODEL_SAML11D14A)

|

||||||

|

#include "vendor/saml11/include/saml11d14a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML11D15A)

|

||||||

|

#include "vendor/saml11/include/saml11d15a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML11D16A)

|

||||||

|

#include "vendor/saml11/include/saml11d16a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML11E14A)

|

||||||

|

#include "vendor/saml11/include/saml11e14a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML11E15A)

|

||||||

|

#include "vendor/saml11/include/saml11e15a.h"

|

||||||

|

#elif defined(CPU_MODEL_SAML11E16A)

|

||||||

|

#include "vendor/saml11/include/saml11e16a.h"

|

||||||

|

|

||||||

|

|

||||||

|

#else

|

||||||

|

#error "Unsupported SAM23 variant."

|

||||||

|

#endif

|

||||||

|

|

||||||

|

/* Workaround redefinition of LITTLE_ENDIAN macro (part2) */

|

||||||

|

#ifdef LITTLE_ENDIAN

|

||||||

|

#undef LITTLE_ENDIAN

|

||||||

|

#endif

|

||||||

|

|

||||||

|

#ifdef __TMP_LITTLE_ENDIAN

|

||||||

|

#define LITTLE_ENDIAN __TMP_LITTLE_ENDIAN

|

||||||

|

#endif

|

||||||

|

|

||||||

|

#ifdef __cplusplus

|

||||||

|

}

|

||||||

|

#endif

|

||||||

|

|

||||||

|

#endif /* SAM23_H */

|

||||||

|

/** @} */

|

||||||

64

cpu/sam0_common/include/vendor/saml10/include/component-version.h

vendored

Normal file

64

cpu/sam0_common/include/vendor/saml10/include/component-version.h

vendored

Normal file

@ -0,0 +1,64 @@

|

|||||||

|

/**

|

||||||

|

* \file

|

||||||

|

*

|

||||||

|

* \brief Component version header file

|

||||||

|

*

|

||||||

|

* Copyright (c) 2018 Atmel Corporation, a wholly owned subsidiary of Microchip Technology Inc.

|

||||||

|

*

|

||||||

|

* \license_start

|

||||||

|

*

|

||||||

|

* \page License

|

||||||

|

*

|

||||||

|

* Licensed under the Apache License, Version 2.0 (the "License");

|

||||||

|

* you may not use this file except in compliance with the License.

|

||||||

|

* You may obtain a copy of the License at

|

||||||

|

*

|

||||||

|

* http://www.apache.org/licenses/LICENSE-2.0

|

||||||

|

*

|

||||||

|

* Unless required by applicable law or agreed to in writing, software

|

||||||

|

* distributed under the License is distributed on an "AS IS" BASIS,

|

||||||

|

* WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

|

||||||

|

* See the License for the specific language governing permissions and

|

||||||

|

* limitations under the License.

|

||||||

|

*

|

||||||

|

* \license_stop

|

||||||

|

*

|

||||||

|

*/

|

||||||

|

|

||||||

|

#ifndef _COMPONENT_VERSION_H_INCLUDED

|

||||||

|

#define _COMPONENT_VERSION_H_INCLUDED

|

||||||

|

|

||||||

|

#define COMPONENT_VERSION_MAJOR 1

|

||||||

|

#define COMPONENT_VERSION_MINOR 0

|

||||||

|

|

||||||

|

//

|

||||||

|

// The COMPONENT_VERSION define is composed of the major and the minor version number.

|

||||||

|

//

|

||||||

|

// The last four digits of the COMPONENT_VERSION is the minor version with leading zeros.

|

||||||

|

// The rest of the COMPONENT_VERSION is the major version.

|

||||||

|

//

|

||||||

|

#define COMPONENT_VERSION 10000

|

||||||

|

|

||||||

|

//

|

||||||

|

// The build number does not refer to the component, but to the build number

|

||||||

|

// of the device pack that provides the component.

|

||||||

|

//

|

||||||

|

#define BUILD_NUMBER 142

|

||||||

|

|

||||||

|

//

|

||||||

|

// The COMPONENT_VERSION_STRING is a string (enclosed in ") that can be used for logging or embedding.

|

||||||

|

//

|

||||||

|

#define COMPONENT_VERSION_STRING "1.0"

|

||||||

|

|

||||||

|

//

|

||||||

|

// The COMPONENT_DATE_STRING contains a timestamp of when the pack was generated.

|

||||||

|

//

|

||||||

|

// The COMPONENT_DATE_STRING is written out using the following strftime pattern.

|

||||||

|

//

|

||||||

|

// "%Y-%m-%d %H:%M:%S"

|

||||||

|

//

|

||||||

|

//

|

||||||

|

#define COMPONENT_DATE_STRING "2018-09-06 14:18:38"

|

||||||

|

|

||||||

|

#endif/* #ifndef _COMPONENT_VERSION_H_INCLUDED */

|

||||||

|

|

||||||

661

cpu/sam0_common/include/vendor/saml10/include/component/ac.h

vendored

Normal file

661

cpu/sam0_common/include/vendor/saml10/include/component/ac.h

vendored

Normal file

@ -0,0 +1,661 @@

|

|||||||

|

/**

|

||||||

|

* \file

|

||||||

|

*

|

||||||

|

* \brief Component description for AC

|

||||||

|

*

|

||||||

|

* Copyright (c) 2018 Microchip Technology Inc.

|

||||||

|

*

|

||||||

|

* \license_start

|

||||||

|

*

|

||||||

|

* \page License

|

||||||

|

*

|

||||||

|

* SPDX-License-Identifier: Apache-2.0

|

||||||

|

*

|

||||||

|

* Licensed under the Apache License, Version 2.0 (the "License");

|

||||||

|

* you may not use this file except in compliance with the License.

|

||||||

|

* You may obtain a copy of the License at

|

||||||

|

*

|

||||||

|

* http://www.apache.org/licenses/LICENSE-2.0

|

||||||

|

*

|

||||||

|

* Unless required by applicable law or agreed to in writing, software

|

||||||

|

* distributed under the License is distributed on an "AS IS" BASIS,

|

||||||

|

* WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

|

||||||

|

* See the License for the specific language governing permissions and

|

||||||

|

* limitations under the License.

|

||||||

|

*

|

||||||

|

* \license_stop

|

||||||

|

*

|

||||||

|

*/

|

||||||

|

|

||||||

|

/* file generated from device description version 2018-08-31T13:51:50Z */

|

||||||

|

#ifndef _SAML10_AC_COMPONENT_H_

|

||||||

|

#define _SAML10_AC_COMPONENT_H_

|

||||||

|

#define _SAML10_AC_COMPONENT_ /**< \deprecated Backward compatibility for ASF */

|

||||||

|

|

||||||

|

/** \addtogroup SAML_SAML10 Analog Comparators

|

||||||

|

* @{

|

||||||

|

*/

|

||||||

|

/* ========================================================================== */

|

||||||

|

/** SOFTWARE API DEFINITION FOR AC */

|

||||||

|

/* ========================================================================== */

|

||||||

|

|

||||||

|

#define AC_U2245 /**< (AC) Module ID */

|

||||||

|

#define REV_AC 0x102 /**< (AC) Module revision */

|

||||||

|

|

||||||

|

/* -------- AC_CTRLA : (AC Offset: 0x00) (R/W 8) Control A -------- */

|

||||||

|

#if !(defined(__ASSEMBLER__) || defined(__IAR_SYSTEMS_ASM__))

|

||||||

|

typedef union {

|

||||||

|

struct {

|

||||||

|

uint8_t SWRST:1; /**< bit: 0 Software Reset */

|

||||||

|

uint8_t ENABLE:1; /**< bit: 1 Enable */

|

||||||

|

uint8_t :6; /**< bit: 2..7 Reserved */

|

||||||

|

} bit; /**< Structure used for bit access */

|

||||||

|

uint8_t reg; /**< Type used for register access */

|

||||||

|

} AC_CTRLA_Type;

|

||||||

|

#endif /* !(defined(__ASSEMBLER__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||||

|

|

||||||

|

#define AC_CTRLA_OFFSET (0x00) /**< (AC_CTRLA) Control A Offset */

|

||||||

|

#define AC_CTRLA_RESETVALUE _U_(0x00) /**< (AC_CTRLA) Control A Reset Value */

|

||||||

|

|

||||||

|

#define AC_CTRLA_SWRST_Pos 0 /**< (AC_CTRLA) Software Reset Position */

|

||||||

|

#define AC_CTRLA_SWRST_Msk (_U_(0x1) << AC_CTRLA_SWRST_Pos) /**< (AC_CTRLA) Software Reset Mask */

|

||||||

|

#define AC_CTRLA_SWRST AC_CTRLA_SWRST_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_CTRLA_SWRST_Msk instead */

|

||||||

|

#define AC_CTRLA_ENABLE_Pos 1 /**< (AC_CTRLA) Enable Position */

|

||||||

|

#define AC_CTRLA_ENABLE_Msk (_U_(0x1) << AC_CTRLA_ENABLE_Pos) /**< (AC_CTRLA) Enable Mask */

|

||||||

|

#define AC_CTRLA_ENABLE AC_CTRLA_ENABLE_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_CTRLA_ENABLE_Msk instead */

|

||||||

|

#define AC_CTRLA_MASK _U_(0x03) /**< \deprecated (AC_CTRLA) Register MASK (Use AC_CTRLA_Msk instead) */

|

||||||

|

#define AC_CTRLA_Msk _U_(0x03) /**< (AC_CTRLA) Register Mask */

|

||||||

|

|

||||||

|

|

||||||

|

/* -------- AC_CTRLB : (AC Offset: 0x01) (/W 8) Control B -------- */

|

||||||

|

#if !(defined(__ASSEMBLER__) || defined(__IAR_SYSTEMS_ASM__))

|

||||||

|

typedef union {

|

||||||

|

struct {

|

||||||

|

uint8_t START0:1; /**< bit: 0 Comparator 0 Start Comparison */

|

||||||

|

uint8_t START1:1; /**< bit: 1 Comparator 1 Start Comparison */

|

||||||

|

uint8_t :6; /**< bit: 2..7 Reserved */

|

||||||

|

} bit; /**< Structure used for bit access */

|

||||||

|

struct {

|

||||||

|

uint8_t START:2; /**< bit: 0..1 Comparator x Start Comparison */

|

||||||

|

uint8_t :6; /**< bit: 2..7 Reserved */

|

||||||

|

} vec; /**< Structure used for vec access */

|

||||||

|

uint8_t reg; /**< Type used for register access */

|

||||||

|

} AC_CTRLB_Type;

|

||||||

|

#endif /* !(defined(__ASSEMBLER__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||||

|

|

||||||

|

#define AC_CTRLB_OFFSET (0x01) /**< (AC_CTRLB) Control B Offset */

|

||||||

|

#define AC_CTRLB_RESETVALUE _U_(0x00) /**< (AC_CTRLB) Control B Reset Value */

|

||||||

|

|

||||||

|

#define AC_CTRLB_START0_Pos 0 /**< (AC_CTRLB) Comparator 0 Start Comparison Position */

|

||||||

|

#define AC_CTRLB_START0_Msk (_U_(0x1) << AC_CTRLB_START0_Pos) /**< (AC_CTRLB) Comparator 0 Start Comparison Mask */

|

||||||

|

#define AC_CTRLB_START0 AC_CTRLB_START0_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_CTRLB_START0_Msk instead */

|

||||||

|

#define AC_CTRLB_START1_Pos 1 /**< (AC_CTRLB) Comparator 1 Start Comparison Position */

|

||||||

|

#define AC_CTRLB_START1_Msk (_U_(0x1) << AC_CTRLB_START1_Pos) /**< (AC_CTRLB) Comparator 1 Start Comparison Mask */

|

||||||

|

#define AC_CTRLB_START1 AC_CTRLB_START1_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_CTRLB_START1_Msk instead */

|

||||||

|

#define AC_CTRLB_MASK _U_(0x03) /**< \deprecated (AC_CTRLB) Register MASK (Use AC_CTRLB_Msk instead) */

|

||||||

|

#define AC_CTRLB_Msk _U_(0x03) /**< (AC_CTRLB) Register Mask */

|

||||||

|

|

||||||

|

#define AC_CTRLB_START_Pos 0 /**< (AC_CTRLB Position) Comparator x Start Comparison */

|

||||||

|

#define AC_CTRLB_START_Msk (_U_(0x3) << AC_CTRLB_START_Pos) /**< (AC_CTRLB Mask) START */

|

||||||

|

#define AC_CTRLB_START(value) (AC_CTRLB_START_Msk & ((value) << AC_CTRLB_START_Pos))

|

||||||

|

|

||||||

|

/* -------- AC_EVCTRL : (AC Offset: 0x02) (R/W 16) Event Control -------- */

|

||||||

|

#if !(defined(__ASSEMBLER__) || defined(__IAR_SYSTEMS_ASM__))

|

||||||

|

typedef union {

|

||||||

|

struct {

|

||||||

|

uint16_t COMPEO0:1; /**< bit: 0 Comparator 0 Event Output Enable */

|

||||||

|

uint16_t COMPEO1:1; /**< bit: 1 Comparator 1 Event Output Enable */

|

||||||

|

uint16_t :2; /**< bit: 2..3 Reserved */

|

||||||

|

uint16_t WINEO0:1; /**< bit: 4 Window 0 Event Output Enable */

|

||||||

|

uint16_t :3; /**< bit: 5..7 Reserved */

|

||||||

|

uint16_t COMPEI0:1; /**< bit: 8 Comparator 0 Event Input Enable */

|

||||||

|

uint16_t COMPEI1:1; /**< bit: 9 Comparator 1 Event Input Enable */

|

||||||

|

uint16_t :2; /**< bit: 10..11 Reserved */

|

||||||

|

uint16_t INVEI0:1; /**< bit: 12 Comparator 0 Input Event Invert Enable */

|

||||||

|

uint16_t INVEI1:1; /**< bit: 13 Comparator 1 Input Event Invert Enable */

|

||||||

|

uint16_t :2; /**< bit: 14..15 Reserved */

|

||||||

|

} bit; /**< Structure used for bit access */

|

||||||

|

struct {

|

||||||

|

uint16_t COMPEO:2; /**< bit: 0..1 Comparator x Event Output Enable */

|

||||||

|

uint16_t :2; /**< bit: 2..3 Reserved */

|

||||||

|

uint16_t WINEO:1; /**< bit: 4 Window x Event Output Enable */

|

||||||

|

uint16_t :3; /**< bit: 5..7 Reserved */

|

||||||

|

uint16_t COMPEI:2; /**< bit: 8..9 Comparator x Event Input Enable */

|

||||||

|

uint16_t :2; /**< bit: 10..11 Reserved */

|

||||||

|

uint16_t INVEI:2; /**< bit: 12..13 Comparator x Input Event Invert Enable */

|

||||||

|

uint16_t :2; /**< bit: 14..15 Reserved */

|

||||||

|

} vec; /**< Structure used for vec access */

|

||||||

|

uint16_t reg; /**< Type used for register access */

|

||||||

|

} AC_EVCTRL_Type;

|

||||||

|

#endif /* !(defined(__ASSEMBLER__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||||

|

|

||||||

|

#define AC_EVCTRL_OFFSET (0x02) /**< (AC_EVCTRL) Event Control Offset */

|

||||||

|

#define AC_EVCTRL_RESETVALUE _U_(0x00) /**< (AC_EVCTRL) Event Control Reset Value */

|

||||||

|

|

||||||

|

#define AC_EVCTRL_COMPEO0_Pos 0 /**< (AC_EVCTRL) Comparator 0 Event Output Enable Position */

|

||||||

|

#define AC_EVCTRL_COMPEO0_Msk (_U_(0x1) << AC_EVCTRL_COMPEO0_Pos) /**< (AC_EVCTRL) Comparator 0 Event Output Enable Mask */

|

||||||

|

#define AC_EVCTRL_COMPEO0 AC_EVCTRL_COMPEO0_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_EVCTRL_COMPEO0_Msk instead */

|

||||||

|

#define AC_EVCTRL_COMPEO1_Pos 1 /**< (AC_EVCTRL) Comparator 1 Event Output Enable Position */

|

||||||

|

#define AC_EVCTRL_COMPEO1_Msk (_U_(0x1) << AC_EVCTRL_COMPEO1_Pos) /**< (AC_EVCTRL) Comparator 1 Event Output Enable Mask */

|

||||||

|

#define AC_EVCTRL_COMPEO1 AC_EVCTRL_COMPEO1_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_EVCTRL_COMPEO1_Msk instead */

|

||||||

|

#define AC_EVCTRL_WINEO0_Pos 4 /**< (AC_EVCTRL) Window 0 Event Output Enable Position */

|

||||||

|

#define AC_EVCTRL_WINEO0_Msk (_U_(0x1) << AC_EVCTRL_WINEO0_Pos) /**< (AC_EVCTRL) Window 0 Event Output Enable Mask */

|

||||||

|

#define AC_EVCTRL_WINEO0 AC_EVCTRL_WINEO0_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_EVCTRL_WINEO0_Msk instead */

|

||||||

|

#define AC_EVCTRL_COMPEI0_Pos 8 /**< (AC_EVCTRL) Comparator 0 Event Input Enable Position */

|

||||||

|

#define AC_EVCTRL_COMPEI0_Msk (_U_(0x1) << AC_EVCTRL_COMPEI0_Pos) /**< (AC_EVCTRL) Comparator 0 Event Input Enable Mask */

|

||||||

|

#define AC_EVCTRL_COMPEI0 AC_EVCTRL_COMPEI0_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_EVCTRL_COMPEI0_Msk instead */

|

||||||

|

#define AC_EVCTRL_COMPEI1_Pos 9 /**< (AC_EVCTRL) Comparator 1 Event Input Enable Position */

|

||||||

|

#define AC_EVCTRL_COMPEI1_Msk (_U_(0x1) << AC_EVCTRL_COMPEI1_Pos) /**< (AC_EVCTRL) Comparator 1 Event Input Enable Mask */

|

||||||

|

#define AC_EVCTRL_COMPEI1 AC_EVCTRL_COMPEI1_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_EVCTRL_COMPEI1_Msk instead */

|

||||||

|

#define AC_EVCTRL_INVEI0_Pos 12 /**< (AC_EVCTRL) Comparator 0 Input Event Invert Enable Position */

|

||||||

|

#define AC_EVCTRL_INVEI0_Msk (_U_(0x1) << AC_EVCTRL_INVEI0_Pos) /**< (AC_EVCTRL) Comparator 0 Input Event Invert Enable Mask */

|

||||||

|

#define AC_EVCTRL_INVEI0 AC_EVCTRL_INVEI0_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_EVCTRL_INVEI0_Msk instead */

|

||||||

|

#define AC_EVCTRL_INVEI1_Pos 13 /**< (AC_EVCTRL) Comparator 1 Input Event Invert Enable Position */

|

||||||

|

#define AC_EVCTRL_INVEI1_Msk (_U_(0x1) << AC_EVCTRL_INVEI1_Pos) /**< (AC_EVCTRL) Comparator 1 Input Event Invert Enable Mask */

|

||||||

|

#define AC_EVCTRL_INVEI1 AC_EVCTRL_INVEI1_Msk /**< \deprecated Old style mask definition for 1 bit bitfield. Use AC_EVCTRL_INVEI1_Msk instead */

|

||||||

|

#define AC_EVCTRL_MASK _U_(0x3313) /**< \deprecated (AC_EVCTRL) Register MASK (Use AC_EVCTRL_Msk instead) */

|

||||||

|

#define AC_EVCTRL_Msk _U_(0x3313) /**< (AC_EVCTRL) Register Mask */

|

||||||

|

|

||||||

|

#define AC_EVCTRL_COMPEO_Pos 0 /**< (AC_EVCTRL Position) Comparator x Event Output Enable */

|

||||||

|

#define AC_EVCTRL_COMPEO_Msk (_U_(0x3) << AC_EVCTRL_COMPEO_Pos) /**< (AC_EVCTRL Mask) COMPEO */

|

||||||

|

#define AC_EVCTRL_COMPEO(value) (AC_EVCTRL_COMPEO_Msk & ((value) << AC_EVCTRL_COMPEO_Pos))

|

||||||

|

#define AC_EVCTRL_WINEO_Pos 4 /**< (AC_EVCTRL Position) Window x Event Output Enable */

|

||||||

|